A7 - Packaging / Encapsulamento

Responsável: Ricardo Cotrin Teixeira

Responsável: Ricardo Cotrin Teixeira

Responsável: José Alexandre Diniz

Responsável: Ricardo Cotrin Teixeira (UNICAMP-CTI)

Email: ricardo.teixeira@cti.gov.br

Resumo: A lei de Moore, estabelecida em 1965, tem sido a força motriz da indústria de semicondutores. Traduzida em 1991 no International Technology Roadmap for Semiconductors (ITRS), direcionou os desenvolvimentos de forma significativa até o ano de 2016, enquanto as regras de escalamento permitiam a redução do tamanho dos circuitos integrados e seus elementos básicos, os transistores. A complexidade dos sistemas eletrônicos levou à substituição do ITRS pelo International Roadmap for Devices and Systems (IRDS) que, desde 2019, é complementado pelo Heterogeneous Integration Roadmap (HIR). Ambos, IRDS e HIR, são mais centrados no desenvolvimento de sistemas multifuncionais ao invés de componentes singulares (leia-se transistores e circuitos integrados), como era o ITRS, trazendo as tecnologias de interconexão e empacotamento eletrônico à tona do desenvolvimento tecnológico e mixando-a com outras formas de produção e tratamento de sinais, como a fotônica e micro/nanosistemas mecânicos (M/NEMS; M/NOEMS – Micro/Nano (Opto) Electro Mechanical Systems).

Tendo em vista este movimento da indústria de semicondutores, bem como experiências anteriores da equipe de Empacotamento Eletrônico do CTI Renato Archer (atualmente alocada na Divisão de Montagem, Empacotamento e Integração de Sistemas – DIMES), propomos o desenvolvimento de tecnologias habilitadoras para a área de empacotamento eletrônico avançado e integração híbrida de componentes, com foco especial na integração eletro-fotônica.

Responsável: Henri Ivanov Boudinov (UFRGS-IF)

Email: henry@ufrgs.br

Resumo: A monitorização da pressão intracraniana foi proposta inicialmente na década de 50, entretanto não obteve muita aderência no meio médico. A razão é simples, a solução disponível na época, e até início dos anos 2000, era inserir um cateter no cérebro do paciente, preencher o mesmo com soro fisiológico, transportar o fluido ao meio externo até um equipamento, geralmente com grandes dimensões, que possuía dentro de si um sensor de pressão. Do ponto de vista técnico, é viável medir a pressão intracraniana desta forma, entretanto, como todas as decisões na medicina, era necessário avaliar a relação risco versus benefício. Neste caso, o risco de infeções letais, tais como encefalite, era muito maior do que o benefício desta técnica. Outro aspecto negativo era o difícil manuseio do paciente, que precisava estar sedado e imóvel. Durante décadas a ideia de monitorar a pressão intracraniana (PIC) foi utilizada somente em casos muito específicos. Por volta dos anos 2000, com o surgimento das técnicas de micro fabricação de sensores de pressão do tipo MEMS, foi possível miniaturizar a eletrônica a colocá-la na ponta do cateter. Desta forma, somente fios elétricos muito finos sairiam da cabeça do paciente, sendo possível eliminar qualquer contato com líquido cefalorraquidiano (LCR) com o meio externo. Atualmente existem somente quatro empresas no mundo que detém essa técnica de fabricação de cateter com micro transdutor.

Do ponto de vista médico, a monitorização de PIC em tempo real é uma excelente ferramenta para o manejo de pacientes com as seguintes condições clínicas: traumatismo cranioencefálico (TCE) grave, pós-operatório de retirada de tumor cerebral, acidente vascular cerebral hemorrágico (AVCH), entre outras. A principal vantagem da monitorização é prover ao médico o cálculo de Pressão de Perfusão Cerebral (PPC). Essa informação é um indicador indireto, porém extremamente confiável, da perfusão de oxigênio nos tecidos cerebrais. Com esta técnica, agora é possível acompanhar a evolução do paciente com indicadores claros e precisos, o que não era possível no passado, sendo que os médicos tinham que interpretar a evolução do paciente às cegas, sem indicadores precisos.

A presente proposta de projeto propõe-se a desenvolver um cateter para monitorização de pressão e temperaturas intracranianas para inserção subdural ou intraparenquimatosa. Para atender o objetivo, será realizado o projeto de encapsulamento, considerando o uso de materiais biocompatíveis e formatos diferentes da indústria convencional de semicondutores.

Partindo de um chip sensor de pressão comercial, e sensor de temperatura do tipo termistor, também disponível no mercado, com dimensões apropriadas aos requisitos do projeto, será desenvolvido um projeto de encapsulamento de cateter de monitorização com inserção no espaço subdural ou intraparenquimatoso. Os microssensores serão depositados sobre um substrato cerâmico que será desenvolvido com formato adequado ao uso na ponta do cateter. Esse substrato será construído usando a técnica de usinagem e contará com o uso de material cerâmico classificado para uso como implante médico. Esta parte do protótipo terá contato direto com tecidos cerebrais e o LCR. Os microtransdurores serão depositados sobre o substrato cerâmico e as conexões com o meio externo serão feitas através da técnica de solda de fios de ouro por solda termossônica, com a utilização de wire bonder, máquina típica da indústria de encapsulamento de semicondutores. A parte eletrônica receberá um recobrimento de silicone biocompatível, evitando o contato do LCR com a membrana de silício e os fios de ouro. Desta forma, somente o substrato cerâmico e o recobrimento de silicone, ambos biocompatíveis, terão contato com tecidos cerebrais. Por fim, a ponta do cateter será conectada a um tubo de material plástico, também biocompatível, que irá transportar os fios com sinais elétricos para o circuito de instrumentação externo ao cateter. O cateter terá apenas 1,5 mm de diâmetro e poderá ser inserido no cérebro do paciente e vedado na interface com o meio exterior com técnica cirúrgica. Desta forma não haverá, em hipótese alguma, contato dos tecidos cerebrais com o meio externo, praticamente eliminando qualquer chance de infeções virais ou bacterianas.

O sensor de temperatura, citado anteriormente, também possui papel importante no projeto. Ele servirá para dois fins: gerar informações para compensar desvios da medição de pressão por dilatação térmica e para fornecer dados clínicos da temperatura cerebral. Estudos recentes demonstraram que a temperatura intracraniana (TIC) é uma excelente ferramenta para determinação de infeções no parênquima, bem como para determinação de morte cerebral.

Por fim, o protótipo desenvolvido será submetido à testes de bancada.

Responsável: Celso Renato Peter (UNISINOS)

Email: cepeter@unisinos.br

Resumo: Um encapsulamento do tipo WLCSP: Wafer Level Chip Scale Package, ou Encapsulamento da Escala do Chip em Nível de Lâmina é o tipo de encapsulamento que oferece não apenas a menor dimensão possível para o chip encapsulado, mas também excelentes performances térmicas e elétricas. A resistência térmica desse tipo de encapsulamento é menor do que em encapsulamentos convencionais do tipo TSOP, QFP, QFN ou BGA.

Neste tipo de encapsulamento o “die” ou chip de silício é diretamente conectado à placa de uso ou aplicação final por meio de esferas de solda ou pilares de cobre, portanto, não há bases metálicas (lead frames) ou substratos intermediários entre o chip e a placa final, esse contato direto facilita a remoção de calor e transferência de sinal com menor latência (menor atraso na propagação), além de reduzir a área do encapsulamento.

As trilhas de interconexão entre as esferas de solda, ou pilares de cobre, com o silício, denominadas trilhas de redistribuição ou redistribution layers (RL), são fabricadas empregando-se técnicas de fabricação de chips diretamente nas lâminas de silício, por isso é um processo do tipo Wafer Level.

Em alguns casos, em que a área do chip de silício é pequena, e com muitas conexões, é necessário ampliar a área disponível para a aplicação das esferas de solda ou pilares de cobre. Nesses casos realiza-se um crescimento da área do chip por meio de sobre moldagem de epóxi e o encapsulamento é denominado Fan Out WLCSP ou WLCSP estendido (com conexões estendidas), nos casos em que todos as conexões cabem sobre o chip de silício o encapsulamento é denominado Fan In WLCSP, ou WLCSP do tipo centralizado ou agrupado (com conexões centralizadas).

Embora o contato direto com a placa facilite a transferência de calor e do sinal, também traz alguns desafios de projeto e fabricação. As dimensões são reduzidas (fine pitch), o que exige um processo de fabricação das placas mais preciso. Também ocorre uma concentração maior do calor devido à pequena área dos chips. Por isso é necessária uma nova abordagem de projeto, é necessário levar-se em consideração a geometria e as propriedades térmicas e mecânicas das diferentes camadas de cobre e isolantes das placas de circuito impresso sobre as quais os chips serão montados. É necessário considerar, por exemplo, o número de camadas de cobre (layers) das placas, a largura das trilhas de cobre e o diâmetro das vias e a quantidade de conexões diretas nos planos de terra e alimentação. Em alguns casos é recomendável ampliar-se as áreas de cobre para auxiliar na remoção e redistribuição do calor gerado pelos chips. Isso requer o conhecimento da Resistência Térmica dos encapsulamentos do tipo WLCSP e o conhecimento das características térmicas dos materiais das placas nas quais os chips serão montados. Nem sempre essas características são conhecidas ou informadas com a exatidão requerida, por isso é necessário medi-las para poder realizar simulações e projetos que funcionem adequadamente. Ainda há poucas informações disponíveis sobre a Resistência Térmica de encapsulamentos do tipo WLCSP. Também é necessário avaliar quais as geometrias e empilhamentos de camadas das placas de circuito impresso (stacking) resultam em melhor desempenho térmico da montagem.

No presente projeto pretende-se implantar um método para avaliar de forma simples e rápida a Resistência Térmica de encapsulamentos do tipo WLCSP e empregar os resultados obtidos para validar uma metodologia de simulação e projeto térmico desse tipo de encapsulamento empregando-se a ferramenta COMSOL Multiphysics. Serão empregados 2 chips do tipo WLCSP com diferentes quantidades e dimensões de esferas e diferentes placas de circuito impresso. Os resultados das medidas realimentarão as simulações permitindo ajustes e otimizações nos projetos e a validação da metodologia.

A atividade de Empacotamento Eletrônico (Packaging) teve início na necessidade de se proteger os diminutos circuitos integrados (chips) de intempéries e manuseio enquanto ainda permitindo o acesso às novas capacidades eletrônicas que estes traziam.

Evoluindo em conjunto e em paralelo com os chips semicondutores desde a década de 1950, o empacotamento eletrônico se tornou uma tecnologia à parte e altamente desenvolvida que abrange desde a montagem de semicondutores discretos até sistemas complexos. Por essa razão, muitas vezes vemos o termo Packaging como sinônimo para Integração de Sistemas.

Atualmente, o Packaging engloba um vasto campo de tecnologias necessárias para interconectar os mais diversos componentes a fim de constituírem um sistema completo. Tais componentes possuem diversas naturezas além do eletrônico, tais como mecânicos (por exemplo MEMS, SAW), ópticos e fotônicos (como câmeras, LEDs e fibra óptica), sensores ambientais e biológicos, componentes para IoT entre vários outros. O melhor exemplo disso são os smartphones e tablets, que possuem sensores de movimentos (componentes mecânicos), telas e câmeras fotográficas/filmadoras com lentes de alta qualidade (componentes ópticos) interconectados a poderosos processadores e memória (componentes eletrônicos) para o seu funcionamento. Conectores de fibra óptica empregados para comunicação de internet e TV a cabo são exemplos de componentes fotônicos interconectados a componentes elétricos.

Além de desenvolver as suas próprias tecnologias, o Packaging também adaptou e agregou várias técnicas empregadas originalmente para a fabricação de transistores e demais categorias de microfabricação, como sputtering, corrosões anisotrópicas, entre outras.

Essa multitude de processos e natureza de componentes trouxe ao contexto da indústria eletrônica o conceito de integração híbrida e de More than Moore, ampliando e estendendo* a principal guia de desenvolvimento, a Lei de Moore, para áreas não mapeadas nem imaginadas nos primórdios deste importante setor econômico mundial.

*veja, por exemplo: R. R. Tummala, “Moore’s Law for Packaging to Replace Moore’s Law for ICS,” 2019 Pan Pacific Microelectronics Symposium (Pan Pacific), Kauai, HI, USA, 2019, pp. 1-6, doi: 10.23919/PanPacific.2019.8696409.

A indústria de semicondutores, da qual o Packaging é parte essencial, é a de mais rápido desenvolvimento em toda a história da humanidade. Essa velocidade vem de uma observação empírica realizada na década de 1960 por Gordon Moore, que tabulou o número de transistores em um circuito integrado e constatou que essa quantidade dobrava a cada dois anos (revisado posteriormente para a cada 18 meses). Vários consórcios e protocolos, como o ITRS e IRDS, envolvendo tanto a academia como a indústria de semicondutores foram formados para manter esta taxa de desenvolvimento, conhecida como “Lei de Moore”, que vem se perpetuando, com certas adaptações, até hoje. Apresentamos a seguir algumas imagens para ilustrar este avanço da indústria de semicondutores e, consequentemente, do Packaging.

Os primeiros transistores vendidos comercialmente foram o 2N696 e 2N697, produzidos pela Fairchild Semi-Conductors (utilizava-se um hífen à época).

Fabricados em 1958, já empregando a tecnologia planar, a diferença entre estes transistores bipolares era o ganho de corrente proporcionado por cada um.

Essa diferença, contudo, não era projetada, mas sim, proveniente de variações do processo de fabricação. Após a devida testagem e caracterização, os transistores que apresentavam o maior ganho de corrente recebiam a denominação terminada em 7. Os demais, que apresentavam apenas metade do ganho, recebiam o final 6.

O dispositivo encapsulado tinha um diâmetro de 6mm (1/4 pol) e foram vendidos à IBM por 200USD cada transistor.

Fonte:

Transistor Museum Photo Gallery Fairchild 2N697 Silicon Mesa Transistor (semiconductormuseum.com)

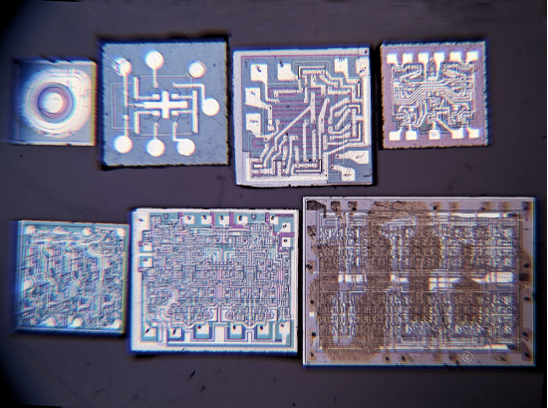

Em 1965 (com uma revisão em 1975) Gordon Moore analisou a quantidade de transistores e o respectivo ano de fabricação de 7 (sete) circuitos integrados para elaborar da lei que recebe o seu nome. A imagem acima mostra os circuitos analisados.

Vale a pena chamar a atenção para a dimensão do primeiro dispositivo, o 2N697, que, sem o encapsulamento, tem um diâmetro de 1,5mm (0,06 pol). O maior chip nesta imagem, 4500 Micromatrix, tem um comprimento de aproximadamente 4,5mm e conta com 264 componentes, entre transistores e resistores. O 4500 ocupa a mesma área que 100 dispositivos RFID atuais (etiquetas eletrônicas, como as usadas em crachás e cartões de crédito), que possuem dezenas de milhares de transistores cada um.

Os dispositivos analisados por Moore e apresentados na imagem são, a partir da esquerda (Tx = transistor; R = resistor):

Superior

– 2N697 planar transistor (1960) – 1 component (1 Tx);

– Micrologic Type G 3-input RTL Gate (1962) – 7 components (3 Tx + 4 R);

– Micrologic Type R RTL Half-Shift Register (late 1962) – 20 components (8 Tx + 12R):

– 945 DTL R-S flip-flop (early 1964) – 33 components (13 Tx + 21R)

Inferior

– 958 Micrologic RTL Decade Counter (late 1964) – 58 components (33 Tx + 25R);

– 9300 TTL Universal shift register (1966) – 125 components (85 Tx + 40R);

– 4500 Micromatrix 32-gate DTL array (1967) – 264 components (200 Tx + 64R).

Fonte:

The Chip Collection – STATE OF THE ART – Smithsonian Institution (si.edu)

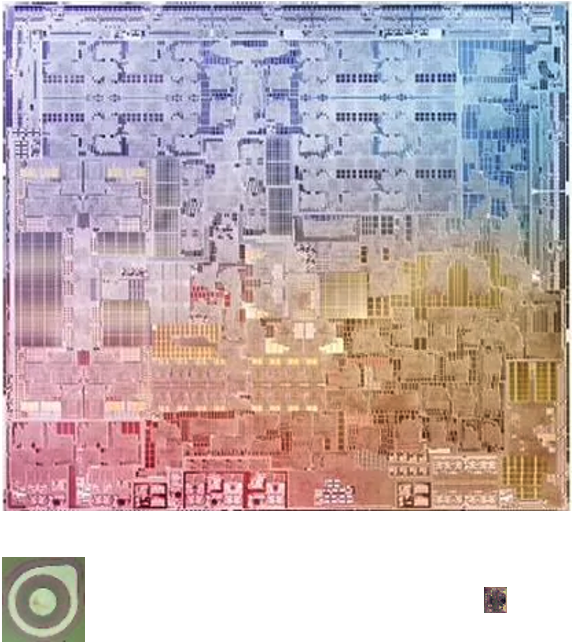

Comparação de tamanhos, em escala aproximada, de diferentes circuitos integrados. Àcima, o processador Apple M2, com tecnologia de 5nm e 20 Bilhões de transistores (2022); abaixo à direita, uma etiqueta eletrônica (RFID Tag) Monza R6 (2015), com cerca de 50.000 transistores e dimensões reais de 0,46 x 0,4 mm (a imagem é 100x maior que o dispositivo original). A imagem à esquerda mostra o primeiro transistor 2N697, com 1,5mm de diâmetro. Esta mesma área (1,5×1,5mm) é suficiente para uma dezena de R6´s ou cerca de 300.000.000 de transistores no Apple M2.

Fontes:

Apple M2 Die Shot and Architecture Analysis – Big Cost Increase And A15 Based IP (semianalysis.com)

Qual a diferença entre o Apple M1 e o Apple M2? Veja comparativo – TecMundo

Inside a RFID race timing chip: die photos of the Monza R6 (righto.com)

O Packaging acompanhou pari passu o avanço da indústria de semicondutores, especializando e desenvolvendo tecnologias para as mais diversas aplicações.

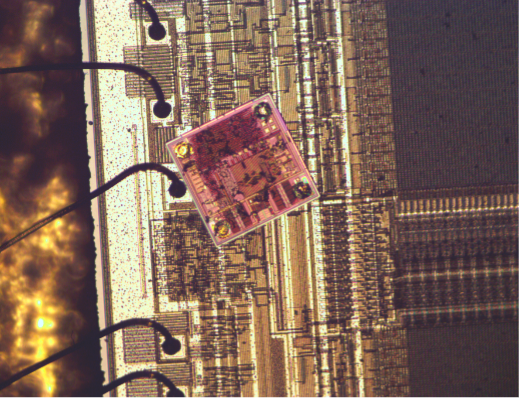

A imagem acima mostra uma etiqueta eletrônica (RFID), empregada na identificação e controle de atletas participantes de uma corrida, contra um micro controlador Intel 8751 ao fundo. Fabricados respectivamente em 2016 e 1983, ambos circuitos são compostos pela mesma ordem de grandeza de transistores, da ordem de 50.000 em cada dispositivo.

Os fios à esquerda são um processo típico da etapa de Packaging chamado wire bonding. Neste caso, o wirebonding foi feito empregando a técnica de ball bonding de microfios de Au, com diâmetro estimado de 25 µm (0,025mm). Atualmente, o diâmetro dos fios foi reduzido até 10µm.

Fonte:

Inside the tiny RFID chip that runs San Francisco’s “Bay to Breakers” race (righto.com)

Além da diminuição do diâmetro dos fios e invólucros (lembrando que o primeiro invólucro, o 2N267, tinha 6mm para um único transistor), diversos materiais e tecnologias foram inseridos no Packaging para garantir tanto a integridade física dos circuitos integrados como a integridade elétrica dos sinais gerados/processados. Etiquetas RFID, como da imagem acima, são interconectadas a antenas para troca de informações com o sistema de leitura/controle de dados em uma selagem hermética à prova d´água, por exemplo.

Estes dispositivos também podem ser encontrados em crachás, caixas automáticos de supermercados e lojas de departamentos, cartões de crédito, aparelhos de TV, celulares, computadores, sensores ambientais e industriais e mais uma infinidade de locais invisíveis de nosso dia a dia. Tudo isso graças ao desenvolvimento das atividades e tecnologias de empacotamento eletrônico.